forked from torvalds/linux

-

Notifications

You must be signed in to change notification settings - Fork 3

LPC18xx LPC43xx clocks

Joachim Eastwood edited this page Oct 24, 2015

·

1 revision

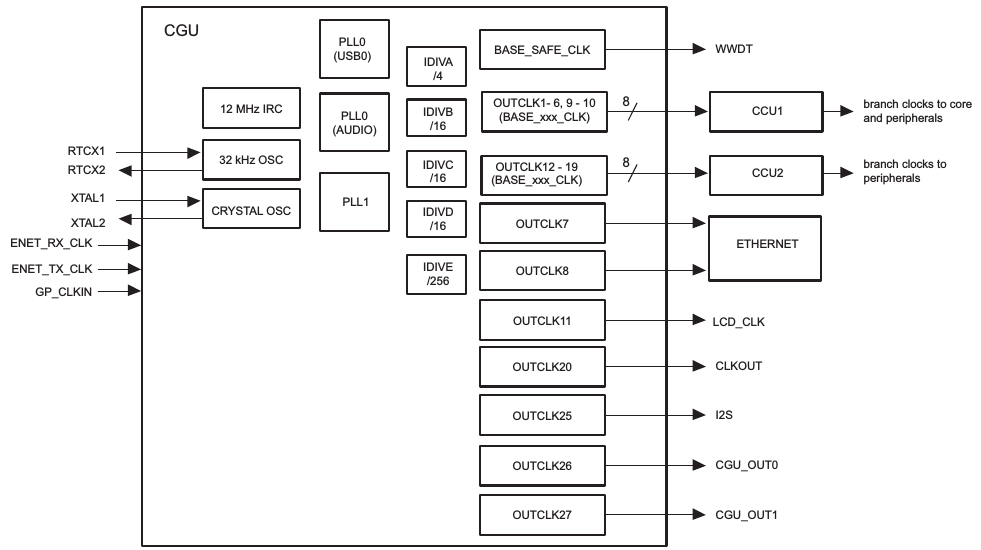

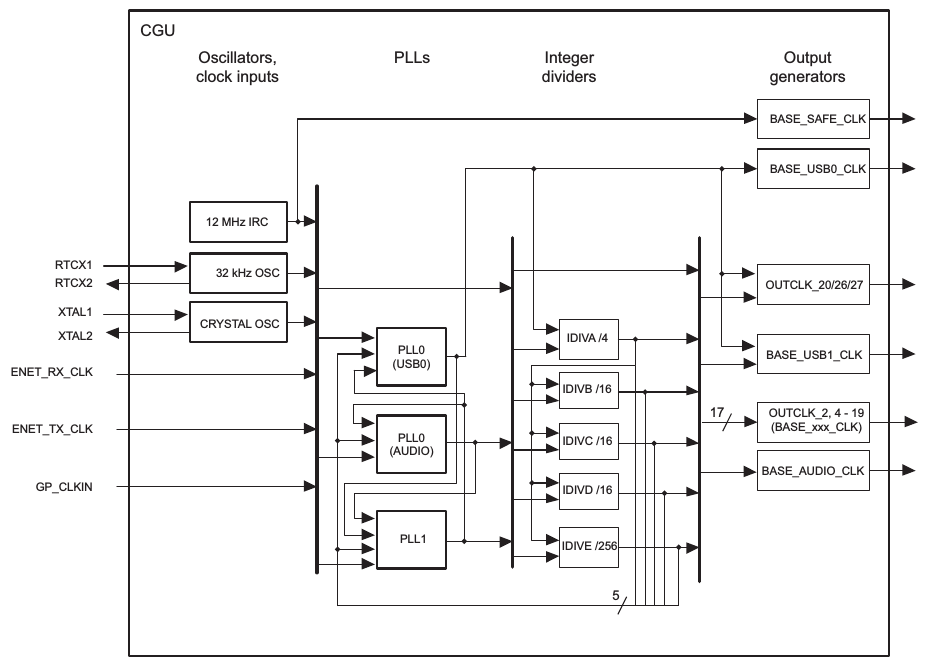

The main clock system on LPC18xx/LPC43xx consist of 3 clock hardware blocks; CGU, CCU1 and CCU2. There is also an additional clock control register in the CREG block that controls the 32 kHz oscillator and the clock for the RTC.

Digaram taken from the NXP LPC43XX User manual (UM10503)

Digaram taken from the NXP LPC43XX User manual (UM10503)

The control registers for the '32 kHz OSC' is not a part of the CGU itself but lives in the CREG block.

Digaram taken from the NXP LPC43XX User manual (UM10503)

Digaram taken from the NXP LPC43XX User manual (UM10503)

Device tree representation

cgu: clock-controller@40050000 {

compatible = "nxp,lpc1850-cgu";

reg = <0x40050000 0x1000>;

#clock-cells = <1>;

clocks = <&xtal>, <&creg_clk 1>, <&enet_rx_clk>, <&enet_tx_clk>, <&gp_clkin>;

};

| Number | Name | Description |

|---|---|---|

| 0 | BASE_SAFE_CLK | Base safe clock (always on) for WWDT |

| 1 | BASE_USB0_CLK | Base clock for USB0 |

| 2 | BASE_PERIPH_CLK | Base clock for Cortex-M0SUB subsystem, SPI, and SGPIO |

| 3 | BASE_USB1_CLK | Base clock for USB1 |

| 4 | BASE_M3/M4_CLK | System base clock for ARM Cortex-M3/M4 core and APB peripheral blocks 0 and 2 |

| 5 | BASE_SPIFI_CLK | Base clock for SPIFI |

| 6 | BASE_SPI_CLK | Base clock for SPI |

| 7 | BASE_PHY_RX_CLK | Base clock for Ethernet PHY Receive clock |

| 8 | BASE_PHY_TX_CLK | Base clock for Ethernet PHY Transmit clock |

| 9 | BASE_APB1_CLK | Base clock for APB peripheral block 1 |

| 10 | BASE_APB3_CLK | Base clock for APB peripheral block 3 |

| 11 | BASE_LCD_CLK | Base clock for LCD |

| 12 | BASE_ADCHS_CLK | Base clock for ADCHS |

| 13 | BASE_SDIO_CLK | Base clock for SD/MMC |

| 14 | BASE_SSP0_CLK | Base clock for SSP0 |

| 15 | BASE_SSP1_CLK | Base clock for SSP1 |

| 16 | BASE_UART0_CLK | Base clock for UART0 |

| 17 | BASE_UART1_CLK | Base clock for UART1 |

| 18 | BASE_UART2_CLK | Base clock for UART2 |

| 19 | BASE_UART3_CLK | Base clock for UART3 |

| 20 | BASE_OUT_CLK | Base clock for CLKOUT pin |

| 21-24 | - | |

| 25 | BASE_AUDIO_CLK | Base clock for audio system (I2S) |

| 26 | BASE_CGU_OUT0_CLK | Base clock for CGU_OUT0 clock output |

| 27 | BASE_CGU_OUT1_CLK | Base clock for CGU_OUT1 clock output |

| Base clock | Branch clock | Description |

|---|---|---|

| BASE_APB3_CLK | CLK_APB3_BUS | |

| CLK_APB3_I2C1 | ||

| CLK_APB3_DAC | ||

| CLK_APB3_ADC0 | ||

| CLK_APB3_ADC1 | ||

| CLK_APB3_CAN0 | ||

| BASE_APB1_CLK | CLK_APB1_BUS | |

| CLK_APB1_MOTOCONPWM | ||

| CLK_APB1_I2C0 | ||

| CLK_APB1_I2S | ||

| CLK_APB1_CAN1 | ||

| BASE_SPIFI_CLK | CLK_SPIFI | |

| BASE_M3/M4_CLK | CLK_M3/M4_BUS | |

| CLK_M3/M4_SPIFI | ||

| CLK_M3/M4_GPIO | ||

| CLK_M3/M4_LCD | ||

| CLK_M3/M4_ETHETNET | ||

| CLK_M3/M4_USB0 | ||

| CLK_M3/M4_EMC | ||

| CLK_M3/M4_SDIO | ||

| CLK_M3/M4_DMA | ||

| CLK_M3/M4_M3/M4CORE | ||

| CLK_M3/M4_SCT | ||

| CLK_M3/M4_USB1 | ||

| CLK_M3/M4_EMC_DIV | ||

| CLK_M3/M4_FLASHA | ||

| CLK_M3/M4_FLASHB | ||

| CLK_M3/M4_M0APP | ||

| CLK_M3/M4_ADCHS | ||

| CLK_M3/M4_EEPROM | ||

| CLK_M3/M4_WWDT | ||

| CLK_M3/M4_UART0 | ||

| CLK_M3/M4_UART1 | ||

| CLK_M3/M4_SSP0 | ||

| CLK_M3/M4_TIMER0 | ||

| CLK_M3/M4_TIMER1 | ||

| CLK_M3/M4_SCU | ||

| CLK_M3/M4_CREG | ||

| CLK_M3/M4_RITIMER | ||

| CLK_M3/M4_UART2 | ||

| CLK_M3/M4_UART3 | ||

| CLK_M3/M4_TIMER2 | ||

| CLK_M3/M4_TIMER3 | ||

| CLK_M3/M4_SSP1 | ||

| CLK_M3/M4_QEI | ||

| BASE_PERIPH_CLK | CLK_PERIPH_BUS | |

| CLK_PERIPH_CORE | ||

| CLK_PERIPH_SGPIO | ||

| BASE_USB0_CLK | CLK_USB0 | |

| BASE_USB1_CLK | CLK_USB1 | |

| BASE_SPI_CLK | CLK_SPI | |

| BASE_ADCHS_CLK | CLK_ADCHS |

Device tree representation

ccu1: clock-controller@40051000 {

compatible = "nxp,lpc1850-ccu";

reg = <0x40051000 0x1000>;

#clock-cells = <1>;

clocks = <&cgu BASE_APB3_CLK>, <&cgu BASE_APB1_CLK>,

<&cgu BASE_SPIFI_CLK>, <&cgu BASE_CPU_CLK>,

<&cgu BASE_PERIPH_CLK>, <&cgu BASE_USB0_CLK>,

<&cgu BASE_USB1_CLK>, <&cgu BASE_SPI_CLK>;

clock-names = "base_apb3_clk", "base_apb1_clk",

"base_spifi_clk", "base_cpu_clk",

"base_periph_clk", "base_usb0_clk",

"base_usb1_clk", "base_spi_clk";

};

| Base clock | Branch clock | Description |

|---|---|---|

| BASE_AUDIO_CLK | CLK_AUDIO | |

| BASE_UART3_CLK | CLK_APB2_UART3 | |

| BASE_UART2_CLK | CLK_APB2_UART2 | |

| BASE_UART1_CLK | CLK_APB0_UART1 | |

| BASE_UART0_CLK | CLK_APB0_UART0 | |

| BASE_SSP1_CLK | CLK_APB2_SSP1 | |

| BASE_SSP0_CLK | CLK_APB0_SSP0 | |

| BASE_SDIO_CLK | CLK_SDIO |

Device tree representation

ccu2: clock-controller@40052000 {

compatible = "nxp,lpc1850-ccu";

reg = <0x40052000 0x1000>;

#clock-cells = <1>;

clocks = <&cgu BASE_AUDIO_CLK>, <&cgu BASE_UART3_CLK>,

<&cgu BASE_UART2_CLK>, <&cgu BASE_UART1_CLK>,

<&cgu BASE_UART0_CLK>, <&cgu BASE_SSP1_CLK>,

<&cgu BASE_SSP0_CLK>, <&cgu BASE_SDIO_CLK>;

clock-names = "base_audio_clk", "base_uart3_clk",

"base_uart2_clk", "base_uart1_clk",

"base_uart0_clk", "base_ssp1_clk",

"base_ssp0_clk", "base_sdio_clk";

};